# Understanding Reduced-Voltage Operation in Modern DRAM Devices: Experimental Characterization, Analysis, and Mechanisms

Kevin K. Chang, Abdullah Giray Yağlıkçı, and Saugata Ghose, Carnegie Mellon University Aditya Agrawal and Niladrish Chatterjee, NVIDIA Abhijith Kashyap, Carnegie Mellon University Donghyuk Lee and Mike O'Connor<sup>\*</sup>, NVIDIA Hasan Hassan and Onur Mutlu<sup>†</sup>, ETH Zürich

In this paper, we take a comprehensive approach to understanding and exploiting the latency and reliability characteristics of modern DRAM when the supply voltage is lowered below the nominal voltage level specified by DRAM standards. Using an FPGA-based testing platform, we perform an experimental study of 124 real DDR3L (low-voltage) DRAM chips manufactured recently by three major DRAM vendors. We find that reducing the supply voltage below a certain point introduces bit errors in the data, and we comprehensively characterize the behavior of these errors. We discover that these errors can be avoided by increasing the latency of three major DRAM operations (activation, restoration, and precharge). We perform detailed DRAM circuit simulations to validate and explain our experimental findings. We also characterize the various relationships between reduced supply voltage and error locations, stored data patterns, DRAM temperature, and data retention.

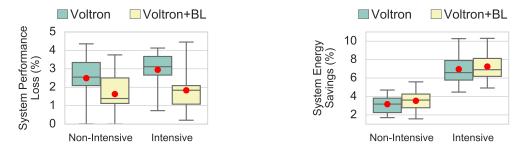

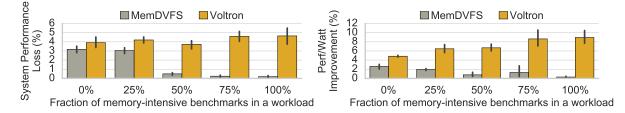

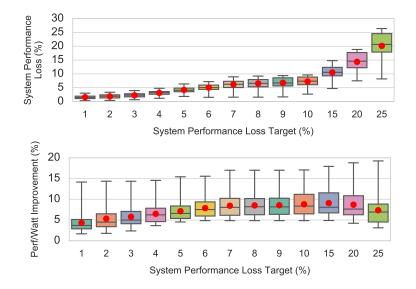

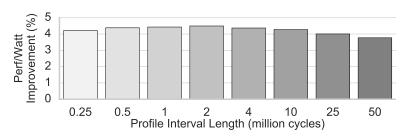

Based on our observations, we propose a new DRAM energy reduction mechanism, called *Voltron*. The key idea of Voltron is to use a performance model to determine by how much we can reduce the supply voltage without introducing errors and without exceeding a user-specified threshold for performance loss. Our evaluations show that Voltron reduces the average DRAM and system energy consumption by 10.5% and 7.3%, respectively, while limiting the average system performance loss to only 1.8%, for a variety of memory-intensive quad-core workloads. We also show that Voltron significantly outperforms prior dynamic voltage and frequency scaling mechanisms for DRAM.

### **ACM Reference format:**

K. K. Chang et al. Understanding Reduced-Voltage Operation in Modern DRAM Devices: Experimental Characterization, Analysis, and Mechanisms. *Proc. ACM Meas. Anal. Comput. Syst.* 1, 1, Article 9 (June 2017), 42 pages.

© 2017 ACM. 2476-1249/2017/6-ART9 \$15.00 DOI: http://dx.doi.org/10.1145/3084447

The energy consumption of DRAM is a critical concern in modern computing systems. Improvements in manufacturing process technology have allowed DRAM vendors to lower the DRAM supply voltage conservatively, which reduces some of the DRAM energy consumption. We would like to reduce the DRAM supply voltage more aggressively, to further reduce energy. Aggressive supply voltage reduction requires a thorough understanding of the effect voltage scaling has on DRAM access latency and DRAM reliability.

<sup>\*</sup>Also with The University of Texas at Austin.

<sup>&</sup>lt;sup>†</sup>Also with Carnegie Mellon University.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.ore.

## 9:2 • K. K. Chang et al.

### **1** INTRODUCTION

In a wide range of modern computing systems, spanning from warehouse-scale data centers to mobile platforms, energy consumption is a first-order concern [26, 32, 35, 45, 55, 87, 95, 101, 138]. In these systems, the energy consumed by the DRAM-based main memory system constitutes a significant fraction of the total energy. For example, experimental studies of production systems have shown that DRAM consumes 40% of the total energy in servers [45, 134] and 40% of the total power in graphics cards [108].

The energy consumed by DRAM is correlated with the *supply voltage* used within the DRAM chips. The supply voltage is distributed to the two major components within DRAM: the *DRAM array* and the *peripheral circuitry* [73, 132]. The DRAM array consists of thousands of capacitor-based DRAM cells, which store data as charge within the capacitor. Accessing data stored in the *DRAM array* requires a DRAM chip to perform a series of fundamental operations: activation, restoration, and precharge.<sup>1</sup> A memory controller orchestrates each of the DRAM operations while obeying the DRAM timing parameters. On the other hand, the *peripheral circuitry* consists of control logic and I/O drivers that connect the DRAM array to the memory channel, which is responsible for transferring commands and data between the memory controller and the DRAM chip. Since the DRAM supply voltage is distributed to both the DRAM array and the peripheral circuitry, changing the supply voltage would affect the energy consumption of both components in the entire DRAM chip.

To reduce the energy consumed by DRAM, vendors have developed low-voltage variants of DDR (Double Data Rate) memory, such as LPDDR4 (Low-Power DDR4) [52] and DDR3L (DDR3 Low-voltage) [51]. For example, in DDR3L, the internal architecture remains the same as DDR3 DRAM, but vendors lower the nominal supply voltage to both the DRAM array and the peripheral circuitry via improvements in manufacturing process technology. In this work, we would like to reduce DRAM energy by *further reducing DRAM supply voltage*. Vendors choose a conservatively high supply voltage, to provide a *guardband* that allows DRAM chips with worst-case process variation to operate without errors under the worst-case operating conditions [32]. The exact amount of supply voltage guardband varies across chips, and lowering the voltage below the guardband can result in erroneous or even undefined behavior. Therefore, we need to understand how DRAM chips behave during reduced-voltage operation. To our knowledge, no previously published work examines the effect of using a wide range of different supply voltage values on the reliability, latency, and retention characteristics of DRAM chips.

**Our goal** in this work is to (*i*) characterize and understand the relationship between supply voltage reduction and various characteristics of DRAM, including DRAM reliability, latency, and data retention; and (*ii*) use the insights derived from this characterization and understanding to design a new mechanism that can aggressively lower the supply voltage to reduce DRAM energy consumption while keeping performance loss under a bound. To this end, we build an FPGA-based testing platform that allows us to tune the DRAM supply voltage [43]. Using this testing platform, we perform experiments on 124 real DDR3L DRAM chips [51] from three major vendors, contained within 31 dual in-line memory modules (DIMMs). Our comprehensive experimental characterization provides four major observations on how DRAM latency, reliability, and data retention time are affected by reduced supply voltage.

First, we observe that we can reliably access data when DRAM supply voltage is lowered below the nominal voltage, *until a certain voltage value*,  $V_{min}$ , which is the minimum voltage level at which no bit errors occur. Furthermore, we find that we can reduce the voltage below  $V_{min}$  to attain further energy savings, but that errors start occurring in some of the data read from memory. As we drop the voltage further below  $V_{min}$ , the number of erroneous bits of data increases exponentially with the voltage drop.

Second, we observe that while reducing the voltage below  $V_{min}$  introduces bit errors in the data, we can prevent these errors if we *increase* the latency of the three fundamental DRAM operations (activation, restoration, and precharge). When the supply voltage is reduced, the capacitor charge takes a longer time to change, thereby

<sup>&</sup>lt;sup>1</sup>We explain the detail of each of these operations in Section 2.

Proc. ACM Meas. Anal. Comput. Syst., Vol. 1, No. 1, Article 9. Publication date: June 2017.

causing these DRAM operations to become slower to complete. Errors are introduced into the data when the memory controller does *not* account for this slowdown in the DRAM operations. We find that if the memory controller allocates extra time for these operations to finish when the supply voltage is below  $V_{min}$ , errors no longer occur. We validate, analyze, and explain this behavior using detailed circuit-level simulations.

Third, we observe that when only a small number of errors occur due to reduced supply voltage, these errors tend to *cluster* physically in certain *regions* of a DRAM chip, as opposed to being randomly distributed throughout the chip. This observation implies that when we reduce the supply voltage to the DRAM array, we need to increase the fundamental operation latencies for *only* the regions where errors can occur.

Fourth, we observe that reducing the supply voltage does *not* impact the data retention guarantees of DRAM. Commodity DRAM chips guarantee that all cells can safely retain data for 64ms, after which the cells are *refreshed* to replenish charge that leaks out of the capacitors. Even when we reduce the supply voltage, the rate at which charge leaks from the capacitors is so slow that no data is lost during the 64ms refresh interval at 20°C and 70°C ambient temperature.

Based on our experimental observations, we propose a new low-cost DRAM energy reduction mechanism called *Voltron*. The key idea of Voltron is to use a performance model to determine by how much we can reduce the DRAM array voltage at runtime without introducing errors and without exceeding a user-specified threshold for acceptable performance loss. Voltron consists of two components: *array voltage scaling* and *performance-aware voltage control*.

*Array voltage scaling* leverages minimal hardware modifications within DRAM to reduce the voltage of *only* the DRAM array, without affecting the voltage of the peripheral circuitry. If Voltron were to reduce the voltage of the peripheral circuitry, we would have to reduce the operating frequency of DRAM. This is because the *maximum* operating frequency of DRAM is a function of the peripheral circuitry voltage [32]. A reduction in the operating frequency reduces the memory data throughput, which can significantly harm the performance of applications that require high memory bandwidth, as we demonstrate in this paper.

*Performance-aware voltage control* uses performance counters within the processor to build a piecewise linear model of how the performance of an application decreases as the DRAM array supply voltage is lowered (due to longer operation latency to prevent errors), and uses the model to select a supply voltage that keeps performance above a user/system-specified performance target.

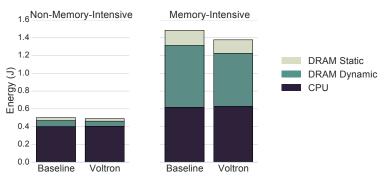

Our evaluations of Voltron show that it significantly reduces both DRAM and system energy consumption, at the expense of very modest performance degradation. For example, at an average performance loss of only 1.8% over seven memory-intensive quad-core workloads from SPEC2006, Voltron reduces DRAM energy consumption by an average of 10.5%, which translates to an overall system energy consumption of 7.3%. We also show that Voltron effectively saves DRAM and system energy on even non-memory-intensive applications, with very little performance impact.

This work makes the following major contributions:

- We perform the first detailed experimental characterization of how the reliability and latency of modern DRAM chips are affected when the supply voltage is lowered below the nominal voltage level. We comprehensively test and analyze 124 real DRAM chips from three major DRAM vendors. Our characterization reveals four new major observations, which can be useful for developing new mechanisms that improve or better trade off between DRAM energy/power, latency, and/or reliability.

- We experimentally demonstrate that reducing the supply voltage below a certain point introduces bit errors in the data read from DRAM. We show that we can avoid these bit errors by increasing the DRAM access latency when the supply voltage is reduced.

- We propose Voltron, a mechanism that (*i*) reduces the supply voltage to only the DRAM array without affecting the peripheral circuitry, and (*ii*) uses a performance model to select a voltage that does not degrade performance

# 9:4 • K. K. Chang et al.

beyond a chosen threshold. We show that Voltron is effective at improving system energy consumption, with only a small impact on performance.

• We open-source our FPGA-based experimental characterization infrastructure and DRAM circuit simulation infrastructure, used in this paper, for evaluating reduced-voltage operation [3].

# 2 BACKGROUND AND MOTIVATION

In this section, we first provide necessary DRAM background and terminology. We then discuss related work on reducing the voltage and/or frequency of DRAM, to motivate the need for our study.

# 2.1 DRAM Organization

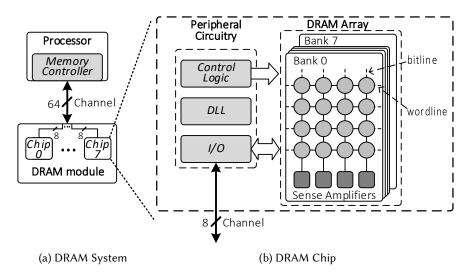

Figure 1a shows a high-level overview of a modern memory system organization. A processor (CPU) is connected to a DRAM module via a *memory channel*, which is a bus used to transfer data and commands between the processor and DRAM. A DRAM module is also called a *dual in-line memory module* (DIMM) and it consists of multiple *DRAM chips*, which are controlled together.<sup>2</sup> Within each DRAM chip, illustrated in Figure 1b, we categorize the internal components into two broad categories: *(i)* the *DRAM array*, which consists of multiple banks of DRAM cells organized into rows and columns, and *(ii) peripheral circuitry*, which consists of the circuits that sit outside of the DRAM array. For a more detailed view of the components in a DRAM chip, we refer the reader to prior works [19–22, 44, 64, 68, 72–76, 78, 84, 114–117, 132].

Fig. 1. DRAM system and chip organization.

A DRAM array is divided into multiple banks (typically eight in DDR3 DRAM [50, 51]) that can process DRAM commands independently from each other to increase parallelism. A bank contains a 2-dimensional array of DRAM cells. Each cell uses a capacitor to store a single bit of data. Each array of cells is connected to a row of sense amplifiers via vertical wires, called *bitlines*. This row of sense amplifiers is called the *row buffer*. The row buffer senses the data stored in one row of DRAM cells and serves as a temporary buffer for the data. A typical row in a DRAM module (i.e., across all of the DRAM chips in the module) is 8KB wide, comprising 128 64-byte cache lines.

<sup>2</sup>In this paper, we study DIMMs that contain a single *rank* (i.e., a group of chips in a single DIMM that operate in lockstep).

The peripheral circuitry has three major components. First, the I/O component is used to receive commands or transfer data between the DRAM chip and the processor via the memory channel. Second, a typical DRAM chip uses a delay-lock loop (DLL) to synchronize its data signal with the external clock to coordinate data transfers on the memory channel. Third, the control logic decodes DRAM commands sent across the memory channel and selects the row and column of cells to read data from or write data into.

# 2.2 Accessing Data in DRAM

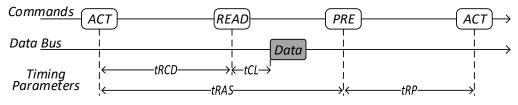

To access data stored in DRAM, the *memory controller* (shown in Figure 1a) issues DRAM commands across the memory channel to the DRAM chips. Reading a cache line from DRAM requires three essential commands, as shown in Figure 2: ACTIVATE, READ, and PRECHARGE. Each command requires some time to complete, and the DRAM standard [51] defines the latency of the commands with a set of *timing parameters*. The memory controller can be programmed to obey different sets of timing parameters through the BIOS [4, 5, 47, 75].

Fig. 2. DRAM commands and timing parameters when reading one cache line of data.

Activate Command. To open the target row of data in the bank that contains the desired cache line, the memory controller first issues an ACTIVATE command to the target DRAM bank. During activation, the electrical charge stored in the target row starts to propagate to the row buffer. The charge propagation triggers the row buffer to latch the data stored in the row after some amount of time. The latency of an ACTIVATE command, or the *activation latency*, is defined as the minimum amount of time that is required to pass from the issue time of an ACTIVATE until the issue time of a column command (i.e., READ or WRITE). The timing parameter for the activation latency is called tRCD, as shown in Figure 2, and is typically set to 13ns in DDR3L [92].

Since an activation drains charge from the target row's cells to latch the cells' data into the row buffer, the cells' charge needs to be restored to prevent data loss. The row buffer performs *charge restoration* simultaneously with activation. Once the cells' charge is fully restored, the row can be closed (and thus the DRAM array be prepared for the next access) by issuing a PRECHARGE command to the DRAM bank. The DRAM standard specifies the restoration latency as the minimum amount of time the controller must wait after ACTIVATE before issuing PRECHARGE. The timing parameter for restoration is called tRAS, as shown in Figure 2, and is typically set to 35ns in DDR3L [92].

**Read Command.** Once the row data is latched in the row buffer after the ACTIVATE command, the memory controller issues a READ command. The row buffer contains multiple cache lines of data (8KB), and the READ command enables all *n* DRAM chips in the DRAM module to select the desired cache line (64B) from the row buffer. Each DRAM chip on the module then drives (1/n)<sup>th</sup> of the cache line from the row buffer to the I/O component within the peripheral circuitry. The peripheral circuitry of each chip then sends its (1/n)<sup>th</sup> of the cache line across the memory channel to the memory controller. Note that the column access time to read and write the cache line is defined by the timing parameters tCL and tCWL, respectively, as shown in Figure 2. Unlike the activation latency (tRCD), tCL and tCWL are *DRAM-internal* timings that are determined by a clock inside DRAM [92]. Therefore, our FPGA-based experimental infrastructure (described in Section 3) *cannot* evaluate the effect of changing tCL and tCWL.

### 9:6 • K. K. Chang et al.

**Precharge Command.** After reading the data from the row buffer, the memory controller may contain a request that needs to access data from a *different* row within the same bank. To prepare the bank to service this request, the memory controller issues a PRECHARGE command to the bank, which closes the currently-activated row and resets the bank in preparation for the next ACTIVATE command. Because closing the activated row and resetting the bank takes some time, the standard specifies the precharge latency as the minimum amount of time the controller must wait for after issuing PRECHARGE before it issues an ACTIVATE. The timing parameter for precharge is called tRP, as shown in Figure 2, and is typically set to 13ns in DDR3L [92].

# 2.3 Effect of DRAM Voltage and Frequency on Power Consumption

DRAM power is divided into dynamic and static power. Dynamic power is the power consumed by executing the access commands: ACTIVATE, PRECHARGE, and READ/WRITE. Each ACTIVATE and PRECHARGE consumes power in the DRAM array and the peripheral circuitry due to the activity in the DRAM array and control logic. Each READ/WRITE consumes power in the DRAM array by accessing data in the row buffer, and in the peripheral circuitry by driving data on the channel. On the other hand, static power is the power that is consumed *regardless* of the DRAM accesses, and it is mainly due to transistor leakage. DRAM power is governed by both the supply voltage and operating clock frequency: *Power*  $\propto$  *Voltage*<sup>2</sup> × *Frequency* [32]. As shown in this equation, power consumption scales quadratically with supply voltage, and linearly with frequency.

DRAM supply voltage is distributed to both the DRAM array and the peripheral circuitry through respective power pins on the DRAM chip, dedicated separately to the DRAM array and the peripheral circuitry. We call the voltage supplied to the DRAM array,  $V_{array}$ , and the voltage supplied to the peripheral circuitry,  $V_{peri}$ . Each DRAM standard requires a specific nominal supply voltage value, which depends on many factors, such as the architectural design and process technology. In this work, we focus on the widely used DDR3L DRAM design that requires a nominal supply voltage of 1.35V [51]. To remain operational when the supply voltage is unstable, DRAM can tolerate a small amount of deviation from the nominal supply voltage. In particular, DDR3L DRAM is specified to operate with a supply voltage ranging from 1.283V to 1.45V [92].

The DRAM channel frequency value of a DDR DRAM chip is typically specified using the *channel data rate*, measured in mega-transfers per second (MT/s). The size of each data transfer is dependent on the width of the data bus, which ranges from 4 to 16 bits for a DDR3L chip [92]. Since a modern DDR channel transfers data on both the positive and the negative clock edges (hence the term *double data rate*, or DDR), the channel frequency is *half of the data rate*. For example, a DDR data rate of 1600 MT/s means that the frequency is 800 MHz. To run the channel at a specified data rate, the peripheral circuitry requires a certain minimum voltage ( $V_{peri}$ ) for stable operation. As a result, the supply voltage scales directly (i.e., linearly) with DRAM frequency, and it determines the maximum operating frequency [32, 35].

# 2.4 Memory Voltage and Frequency Scaling

One proposed approach to reducing memory energy consumption is to scale the voltage and/or the frequency of DRAM based on the observed memory channel utilization. We briefly describe two different ways of scaling frequency and/or voltage below.

**Frequency Scaling.** To enable the power reduction that comes with reduced DRAM frequency, prior works propose to apply *dynamic frequency scaling* (DFS) by adjusting the DRAM channel frequency based on the memory bandwidth demand from the DRAM channel [14, 33–35, 108, 127]. A major consequence of lowering the frequency is the likely performance loss that occurs, as it takes a longer time to transfer data across the DRAM channel while operating at a lower frequency. The clocking logic within the peripheral circuitry requires a *fixed number of DRAM cycles* to transfer the data, since DRAM sends data on each edge of the clock cycle. For a 64-bit memory channel with a 64B cache line size, the transfer typically takes four DRAM cycles [50]. Since lowering the frequency increases the time required for each cycle, the total amount of time spent on data transfer,

in nanoseconds, increases accordingly. As a result, not only does memory latency increase, but also memory data throughput decreases, making DFS undesirable to use when the running workload's memory bandwidth demand or memory latency sensitivity is high. The extra transfer latency from DRAM can also cause longer queuing times for requests waiting at the memory controller [48, 60, 61, 70, 125, 126], further exacerbating the performance loss and potentially delaying latency-critical applications [32, 35].

**Voltage and Frequency Scaling.** While decreasing the channel frequency reduces the peripheral circuitry power and static power, it does *not* affect the dynamic power consumed by the operations performed on the DRAM array (i.e., activation, restoration, precharge). This is because DRAM array operations are asynchronous, i.e., independent of the channel frequency [91]. As a result, these operations require a fixed time (in nanoseconds) to complete. For example, the activation latency in a DDR3L DRAM module is 13ns, regardless of the DRAM frequency [92]. If the channel frequency is doubled from 1066 MT/s to 2133 MT/s, the memory controller doubles the number of cycles for the ACTIVATE timing parameter (i.e., tRCD) (from 7 cycles to 14 cycles), to maintain the 13ns latency.

In order to reduce the dynamic power consumption of the DRAM array as well, prior work proposes *dynamic voltage and frequency scaling* (DVFS) for DRAM, which reduces the supply voltage along with the channel frequency [32]. This mechanism selects a DRAM frequency based on the current memory bandwidth utilization and finds the *minimum operating voltage* ( $V_{min}$ ) for that frequency.  $V_{min}$  is defined to be the lowest voltage that still provides "stable operation" for DRAM (i.e., no errors occur within the data). There are two significant limitations for this proposed DRAM DVFS mechanism. The first limitation is due to a lack of understanding of how voltage scaling affects the DRAM behavior. No prior work provides experimental characterization or analysis of the effect of reducing the DRAM supply voltage on latency, reliability, and data retention in real DRAM chips. As the DRAM behavior under reduced-voltage operation is unknown to satisfactorily maintain the latency and reliability of DRAM, the proposed DVFS mechanism [32] can reduce supply voltage only *very conservatively*. The second limitation is that this prior work reduces the supply voltage for stable operation. As a result, DRAM DVFS results in the same performance issues experienced by the DRAM DFS mechanisms. In Section 6.3, we evaluate the main prior work [32] on memory DVFS to quantitatively demonstrate its benefits and limitations.

# 2.5 Our Goal

The goal of this work is to (*i*) experimentally characterize and analyze *real modern DRAM chips* operating at different supply voltage levels, in order to develop a solid and thorough understanding of how reduced-voltage operation affects latency, reliability, and data retention in DRAM; and (*ii*) develop a mechanism that can reduce DRAM energy consumption by reducing DRAM voltage, without having to sacrifice memory data throughput, based on the insights obtained from comprehensive experimental characterization. Understanding how DRAM characteristics change at different voltage levels is imperative not only for enabling memory DVFS in real systems, but also for developing other low-power and low-energy DRAM designs that can effectively reduce the DRAM voltage. We experimentally analyze the effect of reducing supply voltage of modern DRAM chips in Section 4, and introduce our proposed new mechanism for reducing DRAM energy in Section 5.

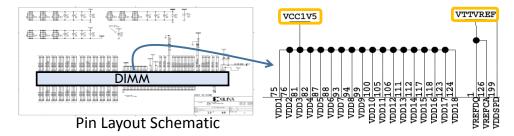

# 3 EXPERIMENTAL METHODOLOGY

To study the behavior of real DRAM chips under reduced voltage, we build an FPGA-based infrastructure based on SoftMC [43], which allows us to have precise control over the DRAM modules. This method was used in many previous works [20, 21, 43, 53, 54, 57–59, 64, 65, 72, 73, 75, 83, 89, 109] as an effective way to explore different DRAM characteristics (e.g., latency, reliability, and data retention time) that have not been known or exposed to the public by DRAM manufacturers. Our testing platform consists of a Xilinx ML605 FPGA board and a host PC that communicates with the FPGA via a PCIe bus (Figure 3). We adjust the supply voltage to the DRAM by using

### 9:8 • K. K. Chang et al.

a USB interface adapter [128] that enables us to tune the power rail connected to the DRAM module directly. The power rail is connected to all the power pins of every chip on the module (as shown in Appendix A).

Fig. 3. FPGA-based DRAM testing platform.

**Characterized DRAM Modules.** In total, we tested 31 DRAM DIMMs, comprising of 124 DDR3L (low-voltage) chips, from the three major DRAM chip vendors that hold more than 90% of the DRAM market share [13]. Each chip has a 4Gb density. Thus, each of our DIMMs has a 2GB capacity. The DIMMs support up to a 1600 MT/s channel frequency. Due to our FPGA's maximum operating frequency limitations, all of our tests are conducted at 800 MT/s. Note that the experiments we perform do *not* require us to adjust the channel frequency. Table 1 describes the relevant information about the tested DIMMs. Appendix E provides detailed information on each DIMM. Unless otherwise specified, we test our DIMMs at an ambient temperature of  $20\pm1^{\circ}$ C. We examine the effects of high ambient temperature (i.e.,  $70\pm1^{\circ}$ C) in Section 4.5.

| Vendor       | Total Number<br>of Chips | Timing (ns)<br>(tRCD/tRP/tRAS) | Assembly<br>Year |

|--------------|--------------------------|--------------------------------|------------------|

| A (10 DIMMs) | 40                       | 13.75/13.75/35                 | 2015-16          |

| B (12 DIMMs) | 48                       | 13.75/13.75/35                 | 2014-15          |

| C (9 DIMMs)  | 36                       | 13.75/13.75/35                 | 2015             |

Table 1. Main properties of the tested DIMMs.

**DRAM Tests.** At a high level, we develop a test (Test 1) that writes/reads data to/from *every* row in the *entire* DIMM, for a given supply voltage. The test takes in several different input parameters: activation latency (tRCD), precharge latency (tRP), and data pattern. The goal of the test is to examine if any errors occur under the given supply voltage with the different input parameters.

In the test, we iteratively test two consecutive rows at a time. The two rows hold data that are the inverse of each other (i.e., *data* and *data*). Reducing tRP lowers the amount of time the precharge unit has to reset the bitline voltage from either *full voltage* (bit value 1) or *zero voltage* (bit value 0) to *half voltage*. If tRP were reduced too much, the bitlines would float at some other intermediate voltage value between *half voltage* and *full/zero*

Understanding Reduced-Voltage Operation in Modern DRAM Devices • 9:9

|   | <b>t 1</b> Test DIMM with specified tRCD/tRP and data particle $\frac{1}{1}$    |                                                   |

|---|---------------------------------------------------------------------------------|---------------------------------------------------|

| 1 | VoltageTest(DIMM, tRCD, tRP, data, data)                                        |                                                   |

| 2 | <b>for</b> bank $\leftarrow 1$ <b>to</b> <i>DIMM.Bank</i> <sub>MAX</sub>        |                                                   |

| 3 | <b>for</b> row $\leftarrow 1$ <b>to</b> <i>bank</i> . <i>Row</i> <sub>MAX</sub> | Walk through every row within the current bank    |

| 4 | <pre>WriteOneRow(bank, row, data)</pre>                                         | Write the data pattern into the current row       |

| 5 | WriteOneRow( $bank, row + 1, \overline{data}$ )                                 | Write the inverted data pattern into the next row |

| 6 | ReadOneRow(tRCD, tRP, bank, row)                                                | ▶ Read the current row                            |

| 7 | ReadOneRow(tRCD, tRP, <i>bank</i> , <i>row</i> + 1)                             | ▷ Read the next row                               |

| 8 | RecordErrors()                                                                  | Count errors in both rows                         |

*voltage.* As a result, the next activation can potentially start before the bitlines are fully precharged. If we were to use the same data pattern in both rows, the sense amplifier would require *less* time to sense the value during the next activation, as the bitline is already *biased* toward those values. By using the *inverse* of the data pattern in the row that is precharged for the next row that is activated, we ensure that the partially-precharged state of the bitlines does *not* unfairly favor the access to the next row [21]. In total, we use three different groups of data patterns for our test: (0x00, 0xff), (0xaa, 0x33), and (0xcc, 0x55). Each specifies the *data* and *data*, placed in consecutive rows in the same bank.

# 4 CHARACTERIZATION OF DRAM UNDER REDUCED VOLTAGE

In this section, we present our major observations from our detailed experimental characterization of 31 commodity DIMMs (124 chips) from three vendors, when the DIMMs operate under reduced supply voltage (i.e., below the nominal voltage level specified by the DRAM standard). First, we analyze the reliability of DRAM chips as we reduce the supply voltage without changing the DRAM access latency (Section 4.1). Our experiments are designed to identify if lowering the supply voltage induces bit errors (i.e., *bit flips*) in data. Second, we present our findings on the effect of increasing the activation and precharge latencies for DRAM operating under reduced supply voltage (Section 4.2). The purpose of this experiment is to understand the trade-off between access latencies (which impact performance) and the supply voltage of DRAM (which impacts energy consumption). We use detailed circuit-level DRAM simulations to validate and explain our observations on the relationship between access latency and supply voltage. Third, we examine the spatial locality of errors induced due to reduced-voltage operation (Section 4.3) and the distribution of errors in the data sent across the memory channel (Section 4.4). Fourth, we study the effect of temperature on reduced-voltage operation (Section 4.5). Fifth, we study the effect of reduced voltage on the data retention times within DRAM (Section 4.6). We present a summary of our findings in Section 4.7.

# 4.1 DRAM Reliability as Supply Voltage Decreases

We first study the reliability of DRAM chips under low voltage, which was not studied by prior works on DRAM voltage scaling (e.g., [32]). For these experiments, we use the minimum activation and precharge latencies that we experimentally determine to be reliable (i.e., they do not induce any errors) under the nominal voltage of 1.35V at  $20\pm1^{\circ}$ C temperature. As shown in prior works [7, 15, 17, 20, 21, 43, 57–59, 72, 73, 75, 81, 84, 106, 107, 109, 131], DRAM manufacturers adopt a pessimistic standard latency that incorporates a large margin as a safeguard to ensure that each chip deployed in the field operates correctly under a wide range of conditions. Examples of these conditions include process variation, which causes some chips or some cells within a chip to be slower than others, or high operating temperatures, which can affect the time required to perform various operations within DRAM. Since our goal is to understand how the inherent DRAM latencies vary with voltage, we conduct our experiments *without* such an excessive margin. We identify that the reliable tRCD and tRP latencies are both 10ns

#### 9:10 • K. K. Chang et al.

(instead of the 13.75ns latency specified by the DRAM standard) at 20°C, which agree with the values reported by prior work on DRAM latency characterization [20, 21, 73, 75].

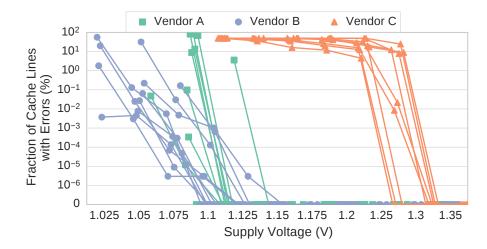

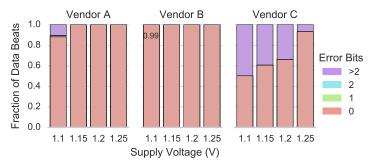

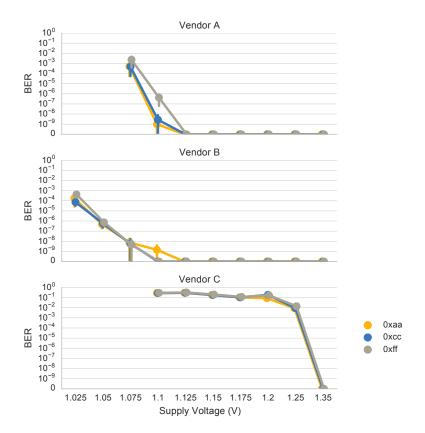

Using the *reliable minimum latency values* (i.e., 10ns for all of the DIMMs), we run Test 1, which accesses every bit within a DIMM at the granularity of a 64B cache line. In total, there are 32 million cache lines in a 2GB DIMM. We vary the supply voltage from the nominal voltage of 1.35V down to 1.20V, using a step size of 0.05V (50mV). Then, we change to a smaller step size of 0.025V (25mV), until we reach the lowest voltage at which the DIMM can operate reliably (i.e., without any errors) while employing the reliable minimum latency values. (We examine methods to further reduce the supply voltage in Section 4.2.) For each voltage step, we run 30 rounds of Test 1 for each DIMM. Figure 4 shows the fraction of cache lines that experience at least 1 bit of error (i.e., 1 bit flip) in each DIMM (represented by each curve), categorized based on vendor.

Fig. 4. The fraction of erroneous cache lines in each DIMM as we reduce the supply voltage, with a fixed access latency.

We make three observations. First, when each DIMM runs below a certain voltage level, errors start occurring. We refer to the *minimum voltage level* of each DIMM that allows error-free operation as  $V_{min}$ . For example, most DIMMs from Vendor C have  $V_{min} = 1.30V$ . Below  $V_{min}$ , we observe errors because the fundamental DRAM array operations (i.e., activation, restoration, precharge) *cannot* fully complete within the time interval specified by the latency parameters (e.g., tRCD, tRAS) at low voltage. Second, not all cache lines exhibit errors for all supply voltage values below  $V_{min}$ . Instead, the number of erroneous cache lines for each DIMM increases as we reduce the voltage further below  $V_{min}$ . Specifically, Vendor A's DIMMs experience a near-exponential increase in errors as the supply voltage reduces below  $V_{min}$ . This is mainly due to the *manufacturing process and architectural variation*, which introduces strength and size variation across the different DRAM cells within a chip [17, 20, 21, 62, 64, 72, 73, 75, 80]. Third, variation in  $V_{min}$  exists not only across DIMMs from the same vendor. However, the variation across DIMMs from the same vendor is much smaller compared to cross-vendor variation, since the fabrication process and circuit designs can differ drastically across vendors. These results demonstrate that reducing voltage beyond  $V_{min}$ , without altering the access latency, has a negative impact on DRAM reliability.

We also conduct an analysis of storing different *data patterns* on the error rate during reduced-voltage operation (see Appendix B). In summary, our results show that the data pattern does *not* have a consistent effect on the rate of errors induced by reduced-voltage operation. For most supply voltage values, the data pattern does *not* have a statistically significant effect on the error rate.

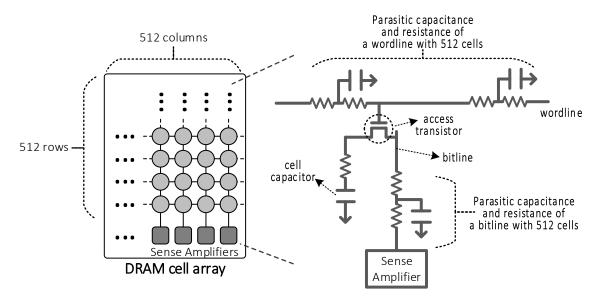

**Source of Errors.** To understand why errors occur in data as the supply voltage reduces below  $V_{min}$ , we perform circuit-level SPICE simulations [88, 102], which reveal more detail on how the cell arrays operate. We develop a SPICE model of the DRAM array that uses a sense amplifier design from prior work [12] with the 45 nm transistor model from the Predictive Technology Model (PTM) [1, 142]. Appendix C provides a detailed description of our SPICE simulation model, which we have open-sourced [3].

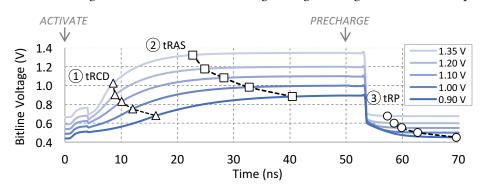

We vary the supply voltage of the DRAM array  $(V_{array})$  in our SPICE simulations from 1.35V to 0.90V. Figure 5 shows the bitline voltage during activation and precharge for different  $V_{array}$  values. Times 0ns and 50ns correspond to when the DRAM receives the ACTIVATE and the PRECHARGE commands, respectively. An ACTIVATE causes the bitline voltage to increase from  $V_{array}/2$  to  $V_{array}$  in order to sense the stored data value of "1". A PRECHARGE resets the bitline voltage back to  $V_{array}/2$  in order to enable the issuing of a later ACTIVATE to another row within the same bank. In the figure, we mark the points where the bitline reaches the (1) *ready-to-access* voltage, which we assume to be 75% of  $V_{array}$ ; (2) *ready-to-precharge* voltage, which we assume to be 98% of  $V_{array}$ ; and (3) *ready-to-activate* voltage, which we assume to be within 2% of  $V_{array}/2$ . These points represent the minimum tRCD, tRAS, and tRP values, respectively, required for reliable DRAM operation. For readers who wish to understand the bitline voltage behavior in more detail, we refer them to recent works [44, 72, 73, 75, 76] that provide extensive background on how the bitline voltage changes during the three DRAM operations.

Fig. 5. Effect of reduced array supply voltage on activation, restoration, and precharge, from SPICE simulations.

We make two observations from our SPICE simulations. First, we observe that the bitline voltage during activation increases at a different rate depending on the supply voltage of the DRAM array ( $V_{array}$ ). Thus, the supply voltage affects the latency of the three DRAM operations (activation, restoration, and precharge). When the nominal voltage level (1.35V) is used for  $V_{array}$ , the time (tRCD) it takes for the sense amplifier to drive the bitline to the *ready-to-access voltage level* (75% of  $V_{array}$ ) is much shorter than the time to do so at a lower  $V_{array}$ . As  $V_{array}$  decreases, the sense amplifier needs more time to latch in the data, increasing the activation latency. Similarly, the restoration latency (tRAS) and the precharge latency (tRP) increase as  $V_{array}$  decreases.

Second, the latencies of the three fundamental DRAM array operations (i.e., activation, restoration, precharge) do *not* correlate with the channel (or clock) frequency (not shown in Figure 5). This is because these operations are clock-independent asynchronous operations that are a function of the cell capacitance, bitline capacitance, and  $V_{array}$  [56].<sup>3</sup> As a result, the channel frequency is *independent* of the three fundamental DRAM operations.

Therefore, we hypothesize that DRAM errors occur at lower supply voltages because the three DRAM array operations have insufficient latency to fully complete at lower voltage levels. In the next section, we experimentally investigate the effect of increasing latency values as we vary the supply voltage on real DRAM chips.

<sup>&</sup>lt;sup>3</sup>In Appendix C, we show a detailed circuit schematic of a DRAM array that operates asynchronously, which forms the basis of our SPICE circuit simulation model [3].

#### 9:12 • K. K. Chang et al.

### 4.2 Longer Access Latency Mitigates Voltage-Induced Errors

To confirm our hypothesis from Section 4.1 that a lower supply voltage requires a longer access latency, we test our DIMMs at supply voltages below the nominal voltage (1.35V) while incrementally increasing the activation and precharge latencies to be as high as 20ns (2x higher than the tested latency in Section 4.1). At each supply voltage value, we call the minimum required activation and precharge latencies that do *not* exhibit any errors  $tRCD_{min}$  and  $tRP_{min}$ , respectively.

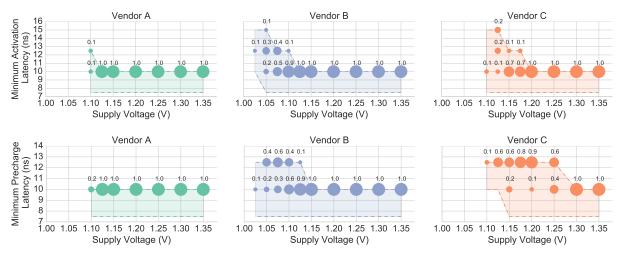

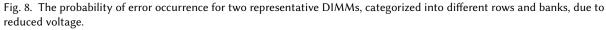

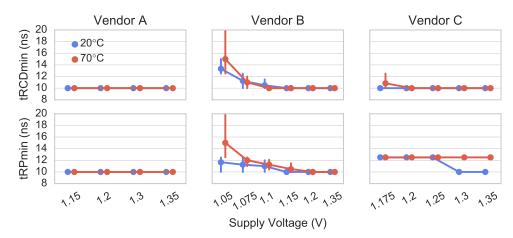

Figure 6 shows the distribution of  $tRCD_{min}$  (top row) and  $tRP_{min}$  (bottom row) measured for all DIMMs across three vendors as we vary the supply voltage. Each circle represents a  $tRCD_{min}$  or  $tRP_{min}$  value. A circle's size indicates the DIMM population size, with bigger circles representing more DIMMs. The number above each circle indicates the fraction of DIMMs that work reliably at the specified voltage and latency. Also, we shade the range of potential  $tRCD_{min}$  and  $tRP_{min}$  values. Since our infrastructure can adjust the latencies at a granularity of 2.5ns, a  $tRCD_{min}$  or  $tRP_{min}$  value of 10ns is only an approximation of the minimum value, as the precise  $tRCD_{min}$  or  $tRP_{min}$  falls between 7.5ns and 10ns. We make three major observations.

Fig. 6. Distribution of minimum reliable latency values as the supply voltage is decreased for 31 DIMMs. The number above each point indicates the fraction of DIMMs that work reliably at the specified voltage and latency. Top row:  $tRCD_{min}$ ; Bottom row:  $tRP_{min}$ .

First, when the supply voltage falls below  $V_{min}^4$ , the tested DIMMs show that an increase of at least 2.5ns is needed for  $tRCD_{min}$  and  $tRP_{min}$  to read data without errors. For example, some DIMMs require at least a 2.5ns increase of  $tRCD_{min}$  or  $tRP_{min}$  to read data without errors at 1.100V, 1.125V, and 1.25V from Vendors A, B, and C, respectively. Since our testing platform can only identify the minimum latency at a granularity of 2.5ns [43], we use circuit-level simulations to obtain a more precise latency measurement of  $tRCD_{min}$  and  $tRP_{min}$  (which we describe in the latter part of this section).

Second, DIMMs from different vendors exhibit very different behavior on how much  $tRCD_{min}$  and  $tRP_{min}$  need to increase for reliable operation as supply voltage falls below  $V_{min}$ . Compared to other vendors, many more of Vendor C's DIMMs require higher  $tRCD_{min}$  and  $tRP_{min}$  to operate at a lower  $V_{array}$ . This is particularly the case for the precharge latency,  $tRP_{min}$ . For instance, 60% of Vendor C's DIMMs require a  $tRP_{min}$  of 12.5ns to read data without errors at 1.25V, whereas this increase is not necessary at all for DIMMs from Vendor A,

<sup>&</sup>lt;sup>4</sup>In Section 4.1, we define  $V_{min}$  as the minimum voltage level of each DIMM that allows error-free operation. Table 7 in Appendix E shows the  $V_{min}$  value we found for each DIMM.

which *all* operate reliably at 1.15V. This reveals that different vendors may have different circuit architectures or manufacturing process technologies, which lead to variations in the additional latency required to compensate for a reduced  $V_{array}$  in DIMMs.

Third, at very low supply voltages, not all of the DIMMs have valid  $tRCD_{min}$  and  $tRP_{min}$  values less than or equal to 20ns that enable error-free operation of the DIMM. We see that the circle size gets smaller as the supply voltage reduces, indicating that the number of DIMMs that can operate reliably (even at higher latency) reduces. For example, Vendor A's DIMMs can no longer operate reliably (i.e., error-free) when the voltage is below 1.1V. We tested a small subset of DIMMs with latencies of more than 50ns and found that these very high latencies still do *not* prevent errors from occurring. We hypothesize that this is because of signal integrity issues on the channel, causing bits to flip during data transfer at very low supply voltages.

We correlate our characterization results with our SPICE simulation results from Section 4.1, demonstrating that there is a direct relationship between supply voltage and access latency. This new observation on the trade-off between supply voltage and access latency is not discussed or demonstrated in prior work on DRAM voltage scaling [32], where the access latency (in nanoseconds) remains *fixed* when performing memory DVFS. In conclusion, we demonstrate both experimentally and in circuit simulations that increasing the access latency (i.e., tRCD and tRP) allows us to lower the supply voltage while still reliably accessing data without errors.

**Deriving More Precise Access Latency Values.** One limitation of our experiments is that we cannot *precisely* measure the *exact*  $tRCD_{min}$  and  $tRP_{min}$  values, due to the 2.5ns minimum latency granularity of our experimental framework [43]. Furthermore, supply voltage is a continuous value, and it would take a prohibitively long time to study the supply voltage experimentally at a finer granularity. We address these limitations by enriching our experimental results with circuit-level DRAM SPICE simulations that model a DRAM array (see Appendix C for details of our circuit simulation model).

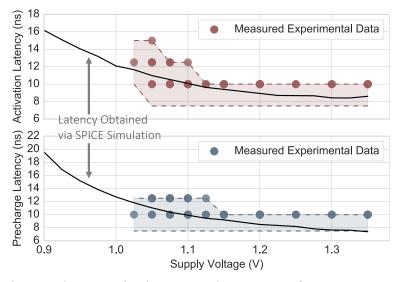

The SPICE simulation results highly depend on the specified transistor parameters (e.g., transistor width). To fit our SPICE results with our experimental results (for the supply voltage values that we studied experimentally), we manually adjust the transistor parameters until the simulated results fit within our *measured* range of latencies. Figure 7 shows the latencies reported for activation and precharge operations using our final SPICE model, based on the measured experimental data for Vendor B.

Fig. 7. SPICE simulation results compared with experimental measurements from 12 DRAM DIMMs for Vendor B.

#### 9:14 • K. K. Chang et al.

We make two major observations. First, we see that the SPICE simulation results fit within the range of latencies measured during our experimental characterization, confirming that our simulated circuit behaves close to the real DIMMs. As a result, our circuit model allows us to derive a more precise minimum latency for reliable operation than our experimental data.<sup>5</sup> Second, DRAM arrays can operate at a wide range of voltage values without experiencing errors. This aligns with our hypothesis that errors at very low supply voltages (e.g., 1V) occur during data transfers across the channel rather than during DRAM array operations. Therefore, our SPICE simulations not only validate our observation that a lower supply voltage requires longer access latency, but also provide us with a more precise reliable minimum operating latency estimate for a given supply voltage.

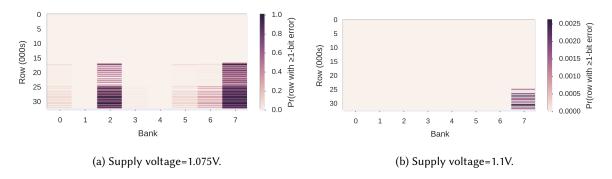

### 4.3 Spatial Locality of Errors

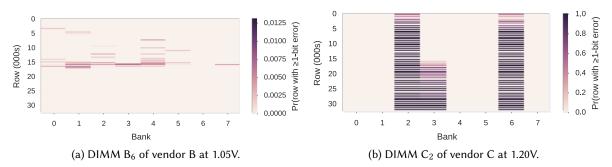

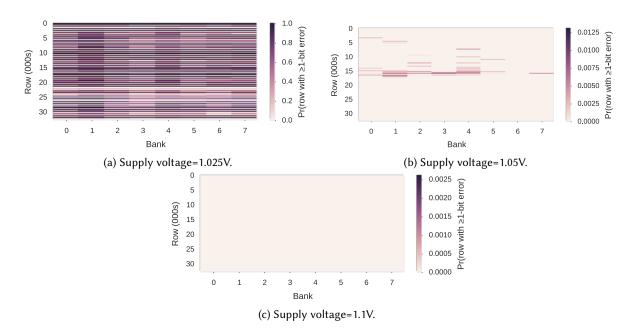

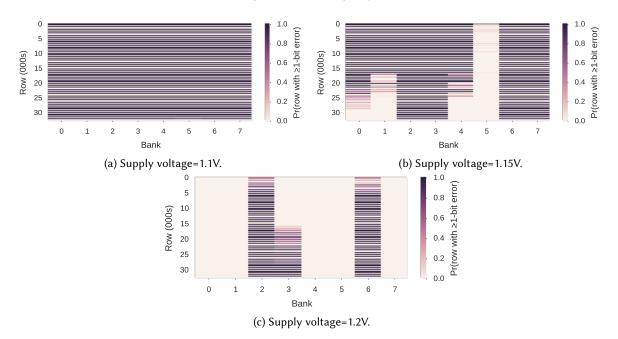

While reducing the supply voltage induces errors when the DRAM latency is not long enough, we also show that not all DRAM locations experience errors at all supply voltage levels. To understand the locality of the errors induced by a low supply voltage, we show the probability of each DRAM row in a DIMM experiencing at least one bit of error across all experiments. We present results for two representative DIMMs from two different vendors, as the observations from these two DIMMs are similar to those we make for the other tested DIMMs. Our results collected from each of the 31 DIMMs are publicly available [3].

Figure 8 shows the probability of each row experiencing at least a one-bit error due to reduced voltage in the two representative DIMMs. For each DIMM, we choose the supply voltage when errors start appearing (i.e., the voltage level one step below  $V_{min}$ ), and we do *not* increase the DRAM access latency (i.e., 10ns for both tRCD and tRP). The x-axis and y-axis indicate the bank number and row number (in thousands), respectively. Our tested DIMMs are divided into eight banks, and each bank consists of 32K rows of cells.<sup>6</sup>

Our main observation is that errors tend to cluster at certain locations. For our representative DIMMs, we see that errors tend to cluster at certain rows across multiple banks for Vendor B. On the contrary, Vendor C's DIMMs exhibit errors in certain banks but not in other banks. We hypothesize that the error concentration can be a result of (*i*) manufacturing process variation, resulting in less robust components at certain locations, as observed in Vendor B's DIMMs; or (*ii*) architectural design variations in the power delivery network. However, it is hard to verify our hypotheses without knowing the specifics of the DRAM circuit design, which is proprietary information that varies across different DRAM models within and across vendors.

Another implication of the spatial concentration of errors under low voltage is that only those regions with errors require a higher access latency to read or write data correctly, whereas error-free regions can be accessed

<sup>&</sup>lt;sup>5</sup>The circuit model can further serve as a common framework for studying other characteristics of DRAM.

<sup>&</sup>lt;sup>6</sup>Additional results showing the error locations at different voltage levels are in Appendix D.

Proc. ACM Meas. Anal. Comput. Syst., Vol. 1, No. 1, Article 9. Publication date: June 2017.

reliably with the standard latency. In Section 6.5, we discuss and evaluate a technique that exploits this spatial locality of errors to improve system performance.

### 4.4 Density of Errors

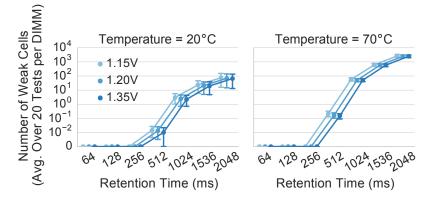

In this section, we investigate the density (i.e., the number) of error bits that occur within each *data beat* (i.e., the unit of data transfer, which is 64 bits, through the data bus) read back from DRAM. Conventional error-correcting codes (ECC) used in DRAM detect and correct errors at the granularity of a data beat. For example, SECDED ECC [85, 122] can correct a single-bit error and detect two-bit errors within a data beat. Figure 9 shows the distribution of data beats that contain no errors, a single-bit error, two-bit errors, or more than two bits of errors, under different supply voltages for all DIMMs. These distributions are collected from 30 rounds of experiments that were tested on each of the 31 DIMMs per voltage level, using 10ns of activation and precharge latency. A round of experiment refers to a single run of Test 1, as described in Section 3, on a specified DIMM.

Fig. 9. Distribution of bit errors in data beats.

The results show that lowering the supply voltage increases the fraction of beats that contain more than two bits of errors. There are very few beats that contain only one or two error bits. This implies that the most commonly-used ECC scheme, SECDED, is unlikely to alleviate errors induced by a low supply voltage. Another ECC mechanism, Chipkill [85, 122], protects multiple bit failures within a DRAM chip. However, it cannot correct errors in *multiple* DRAM chips. Instead, we believe that increasing the access latency, as shown in Section 4.2, is a more effective way of eliminating errors under low supply voltages.

### 4.5 Effect of Temperature

Temperature is an important external factor that can affect the behavior of DRAM [37, 57, 65, 73, 75, 83, 84, 113]. Prior works have studied the impact of temperature on reliability [37, 64, 65, 113], latency [20, 21, 73, 75], and retention time [57, 83, 84, 109] at the nominal supply voltage. However, no prior work has studied the effect of temperature on the latency at which DRAM operates reliably, as the supply voltage changes.

To reduce the test time, we test 13 representative DIMMs under a high ambient temperature of 70°C using a closed-loop temperature controller [43]. Figure 10 shows the  $tRCD_{min}$  and  $tRP_{min}$  values of tested DIMMs, categorized by vendor, at 20°C and 70°C. The error bars indicate the minimum and maximum latency values across all DIMMs we tested that are from the same vendor. We increase the horizontal spacing between the low and high temperature data points at each voltage level to improve readability.

We make two observations. First, temperature impacts vendors differently. On Vendor A's DIMMs, temperature does not have an observable impact on the reliable operation latencies. Since our platform can test latencies with a step size of only 2.5ns, it is possible that the effect of high temperature on the reliable minimum operating latency for Vendor A's DIMMs may be within 2.5ns. On the other hand, the temperature effect on latency is measurable

### 9:16 • K. K. Chang et al.

Fig. 10. Effect of high ambient temperature (70°C) on minimum reliable operation latency at reduced voltage.

on DIMMs from Vendors B and C. DIMMs from Vendor B are not strongly affected by temperature when the supply voltage is above 1.15V. The precharge latency for Vendor C's DIMMs is affected by high temperature at supply voltages of 1.35V and 1.30V, leading to an increase in the minimum latency from 10ns to 12.5ns. When the voltage is below 1.25V, the impact of high temperature on precharge latency is not observable, as the precharge latency already needs to be raised by 2.5ns, to 12.5ns, at 20°C. Second, the precharge latency is more sensitive to temperature than the activation latency. Across all of our tested DIMMs, tRP increases with high temperature under a greater number of supply voltage levels, whereas tRCD is less likely to be perturbed by temperature.

Since temperature can affect latency behavior under different voltage levels, techniques that compensate for temperature changes can be used to dynamically adjust the activation and precharge latencies, as proposed by prior work [73, 75].

### 4.6 Impact on Refresh Rate

Recall from Section 2.1 that a DRAM cell uses a capacitor to store data. The charge in the capacitor leaks over time. To prevent data loss, DRAM periodically performs an operation called *refresh* to restore the charge stored in the cells. The frequency of refresh is determined by the amount of time a cell can retain enough charge without losing information, commonly referred to as a cell's *retention time*. For DDR3 DIMMs, the worst-case retention time assumed for a DRAM cell is 64ms (or 32ms at temperatures above 85°C [83, 84]). Hence, each cell is refreshed every 64ms, which is the DRAM-standard refresh interval.

When we reduce the supply voltage of the DRAM array, we expect the retention time of a cell to *decrease*, as less charge is stored in each cell. This could potentially require a shorter refresh interval (i.e., more frequent refreshes). To investigate the impact of low supply voltage on retention time, our experiment writes all 1s to every cell, and reads out the data after a given amount of retention time, with refresh disabled. We test a total of seven different retention times (in ms): 64 (the standard time), 128, 256, 512, 1024, 1536, and 2048. We conduct the experiment for ten rounds on every DIMM from all three vendors. Figure 11 shows the average number of *weak* cells (i.e., cells that experience bit flips due to too much leakage at a given retention time) across all tested DIMMs, for each retention time, under both 20°C and 70°C. We evaluate three voltage levels, 1.35V, 1.2V, and 1.15V, that allow data to be read reliably with a sufficiently long latency. The error bars indicate the 95% confidence interval. We increase the horizontal spacing between the curves at each voltage level to improve readability.

Fig. 11. The number of weak cells that experience errors under different retention times as supply voltage varies.

Our results show that every DIMM can retain data for at least 256ms before requiring a refresh operation, which is 4x higher than the standard worst-case specification. These results align with prior works, which also experimentally demonstrate that commodity DRAM cells have much higher retention times than the standard specification of 64ms [43, 57, 62, 73, 75, 83, 107, 109]. Even though higher retention times (i.e., longer times without refresh) reveal more weak cells, the number of weak cells is still very small, e.g., tens of weak cells out of billions of cells, on average across all DIMMs at under 20°C. Again, this corresponds closely to observations from prior works showing that there are relatively few weak cells with low retention time in DRAM chips, especially at lower temperatures [43, 57, 62, 73, 75, 83, 107, 109].

We observe that the effect of the supply voltage on retention times is *not* statistically significant. For example, at a 2048ms retention time, the average *number* of weak cells in a DRAM module increases by only 9 cells (out of a population of billions of cells) when the supply voltage drops from 1.35V (66 weak cells) to 1.15V (75 weak cells) at 20°C. For the same 2048ms retention time at 70°C, the average number of weak cells increases by only 131 cells when the supply voltage reduces from 1.35V (2510 weak cells) to 1.15V (2641 weak cells).

When we lower the supply voltage, we do not observe *any* weak cells until a retention time of 512ms, which is 8x the standard refresh interval of 64ms. Therefore, we conclude that using a reduced supply voltage does not require any changes to the standard refresh interval at 20°C and 70°C ambient temperature.

### 4.7 Summary

We have presented extensive characterization results and analyses on DRAM chip latency, reliability, and data retention time behavior under various supply voltage levels. We summarize our findings in six key points. First, DRAM reliability worsens (i.e., more errors start appearing) as we reduce the supply voltage below  $V_{min}$ . Second, we discover that voltage-induced errors occur mainly because, at low supply voltages, the DRAM access latency is no longer sufficient to allow the fundamental DRAM operations to complete. Third, via both experiments on real DRAM chips and SPICE simulations, we show that increasing the latency of activation, restoration, and precharge operations in DRAM can mitigate errors under low supply voltage levels until a certain voltage level. Fourth, we show that voltage-induced errors exhibit strong spatial locality in a DRAM chip, clustering at certain locations (i.e., certain banks and rows). Fifth, temperature affects the reliable access latency at low supply voltage levels and the effect is very vendor-dependent. Sixth, we find that reducing the supply voltage does *not* require increasing the standard DRAM refresh rate for reliable operation below 70°C.

# 9:18 • K. K. Chang et al.

# 5 VOLTRON: REDUCING DRAM ENERGY WITHOUT SACRIFICING MEMORY THROUGHOUT

Based on the extensive understanding we developed on reduced-voltage operation of real DRAM chips in Section 4, we propose a new mechanism called *Voltron*, which reduces DRAM energy without sacrificing memory throughput. Voltron exploits the fundamental observation that reducing the supply voltage to DRAM requires increasing the latency of the three DRAM operations in order to prevent errors. Using this observation, the key idea of Voltron is to use a performance model to determine by how much to reduce the DRAM supply voltage, without introducing errors and without exceeding a user-specified threshold for performance loss. Voltron consists of two main components: *(i) array voltage scaling*, a hardware mechanism that leverages our experimental observations to scale *only* the voltage supplied to the DRAM array; and *(ii) performance-aware voltage control*, a software mechanism<sup>7</sup> that automatically chooses the minimum DRAM array voltage that meets a user-specified performance target.

### 5.1 Array Voltage Scaling

As we discussed in Section 2.3, the DRAM supply voltage to the peripheral circuitry determines the maximum operating frequency. If we reduce the supply voltage directly, the frequency needs to be lowered as well. As more applications become more sensitive to memory bandwidth, reducing DRAM frequency can result in a substantial performance loss due to lower data throughput. In particular, we find that reducing the DRAM frequency from 1600 MT/s to 1066 MT/s significantly degrades performance of our evaluated memory-intensive applications by 16.1%. Therefore, the design challenge of Voltron is to reduce the DRAM supply voltage *without* changing the DRAM frequency.

To address this challenge, the key idea of Voltron's first component, *array voltage scaling*, is to reduce the voltage supplied to the *DRAM array* ( $V_{array}$ ) without changing the voltage supplied to the peripheral circuitry, thereby allowing the DRAM channel to maintain a high frequency while reducing the power consumption of the DRAM array. To prevent errors from occurring during reduced-voltage operation, Voltron increases the latency of the three DRAM operations (activation, restoration, and precharge) in every DRAM bank based on our observations in Section 4.

By reducing  $V_{array}$ , we effectively reduce (*i*) the dynamic DRAM power on activate, precharge, and refresh operations; and (*ii*) the portion of the static power that comes from the DRAM array. These power components decrease *quadratically* with the square of the array voltage reduction in a modern DRAM chip [12, 56]. The trade-off is that reducing  $V_{array}$  requires increasing the latency of the three DRAM operations, for reliable operation, thereby leading to some system performance degradation, which we quantify in our evaluation (Section 6).

# 5.2 Performance-Aware Voltage Control

Array voltage scaling provides system users with the ability to decrease  $V_{array}$  to reduce DRAM power. Employing a lower  $V_{array}$  provides greater power savings, but at the cost of longer DRAM access latency, which leads to larger performance degradation. This trade-off varies widely across different applications, as each application has a different tolerance to the increased memory latency. This raises the question of how to pick a "suitable" array voltage level for different applications as a system user or designer. For this work, we say that an array voltage level is suitable if it does not degrade system performance by more than a user-specified threshold. Our goal is to provide a simple technique that can automatically select a suitable  $V_{array}$  value for different applications. To this end, we propose *performance-aware voltage control*, a power-performance management policy that selects a minimum  $V_{array}$  that satisfies a desired performance constraint. The key observation is that an application's performance loss (due to increased memory latency) scales linearly with the application's memory demand (e.g., memory intensity). Based on this empirical observation we make, we build a *performance loss predictor* that

<sup>&</sup>lt;sup>7</sup>Note that this mechanism can also be implemented in hardware, or as a cooperative hardware/software mechanism.

Proc. ACM Meas. Anal. Comput. Syst., Vol. 1, No. 1, Article 9. Publication date: June 2017.

leverages a linear model to predict an application's performance loss based on its characteristics at runtime. Using the performance loss predictor, Voltron finds a  $V_{array}$  that can keep the predicted performance within a user-specified target at runtime.

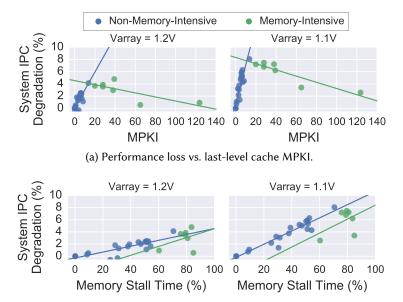

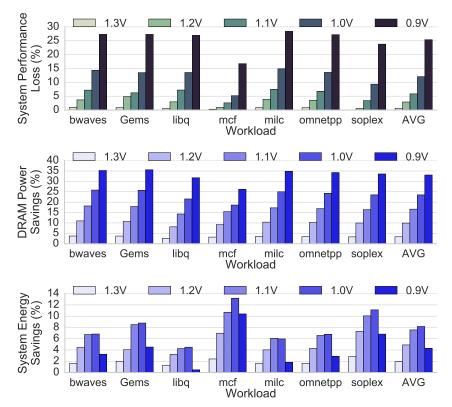

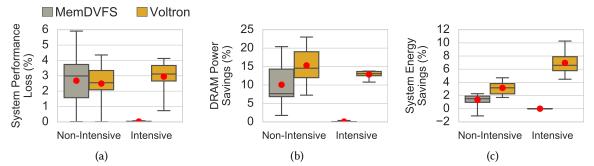

**Key Observation.** We find that an application's performance loss due to higher latency has a strong linear relationship with its memory demand (e.g., memory intensity). Figure 12 shows the relationship between the performance loss of each application (due to reduced voltage) and its memory demand under two different reduced-voltage values (see Section 6.1 for our methodology). Each data point represents a single application. Figure 12a shows each application's performance loss versus its *memory intensity*, expressed using the commonly-used metric MPKI (last-level cache misses per kilo-instruction). Figure 12b shows each application's performance loss versus its *memory requests* stall the CPU's instruction window (i.e., reorder buffer). In Figure 12a, we see that the performance loss is a *piecewise linear function* based on the MPKI. The observation that an application's *sensitivity to memory latency* is correlated with MPKI has also been made and utilized by prior works [29–31, 66, 67, 93, 98, 99, 130, 141, 143].

Fig. 12. Relationship between performance loss (due to increased memory latency) and applications' characteristics: MPKI (a) and memory stall time fraction (b). Each data point represents a single application.

When an application is *not* memory-intensive (i.e., has an MPKI < 15), its performance loss grows linearly with MPKI, becoming *more sensitive* to memory latency. Latency-sensitive applications spend most of their time performing computation at the CPU cores and issue memory requests infrequently. As a result, increasing the number of memory requests causes more stall cycles in the CPU.

On the other hand, the performance of memory-intensive applications (i.e., those with  $MPKI \ge 15$ ) is *less* sensitive to memory latency as the MPKI grows. This is because memory-intensive applications experience frequent cache misses and spend a large portion of their time waiting on pending memory requests. As a result, their rate of progress is significantly affected by the memory bandwidth, and therefore they are more sensitive to memory throughput instead of latency. With more outstanding memory requests (i.e., higher MPKI), the memory

#### 9:20 • K. K. Chang et al.

system is more likely to service them in parallel, leading to more *memory-level parallelism* [41, 67, 71, 94, 99, 100]. Therefore, improved memory-level parallelism enables applications to tolerate higher latencies more easily.

Figure 12b shows that an application's performance loss increases with its instruction window (reorder buffer) *stall time fraction* due to memory requests for both memory-intensive and non-memory-intensive applications. A stalled instruction window prevents the CPU from fetching or dispatching new instructions [100], thereby degrading the running application's performance. This observation has also been made and utilized by prior works [40, 96, 97, 100].

**Performance Loss Predictor.** Based on the observed linear relationships between performance loss vs. MPKI and memory stall time fraction, we use *ordinary least squares (OLS)* regression to develop a piecewise linear model for each application that can serve as the performance loss predictor for Voltron. Equation 1 shows the model, which takes the following inputs: memory latency (*Latency* = tRAS + tRP), the application's MPKI, and its memory stall time fraction.

| Due liste II                         | $ \begin{pmatrix} \alpha_1 + \beta_1 \text{Latency}_i + \beta_2 \text{App.MPKI}_i \\ + \beta_3 \text{App.StallTimeFraction}_i \end{pmatrix} $ | if <i>MPKI</i> < 15 | (1) |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|

| PredictedLoss <sub>i</sub> = $\cdot$ | $ \begin{array}{l} \alpha_2 + \beta_4 \text{Latency}_i + \beta_5 \text{App.MPKI}_i \\ + \beta_6 \text{App.StallTimeFraction}_i \end{array} $  | otherwise           | (1) |

| $\alpha_1$ | $\beta_1$ | $\beta_2$ | $\beta_3$ | $\alpha_2$ | $\beta_4$ | $\beta_5$ | $\beta_6$ |

|------------|-----------|-----------|-----------|------------|-----------|-----------|-----------|

| -30.09     | 0.59      | 0.01      | 19.24     | -50.04     | 1.05      | -0.01     | 15.27     |

PredictedLoss<sub>i</sub> is the predicted performance loss for the application. The subscript *i* refers to each data sample, which describes a particular application's characteristics (MPKI and memory stall time fraction) and the memory latency associated with the selected voltage level. To generate the data samples, we run a total of 27 workloads across 8 different voltage levels that range from 1.35V to 0.90V, at a 50mV step (see Section 6.1 for our methodology). In total, we generate 216 data samples for finding the coefficients (i.e.,  $\alpha$  and  $\beta$  values) in our model. To avoid overfitting the model, we use the *scikit-learn* machine learning toolkit [46] to perform cross-validation, which randomly splits the data samples into a training set (151 samples) and a test set (65 samples). To assess the fit of the model, we use a common metric, root-mean-square error (RMSE), which is 2.8 and 2.5 for the low-MPKI and high-MPKI pieces of the model, respectively. Furthermore, we calculate the R<sup>2</sup> value to be 0.75 and 0.90 for the low-MPKI and high-MPKI models, respectively. Therefore, the RMSE and R<sup>2</sup> metrics indicate that our model provides high accuracy for predicting the performance loss of applications under different  $V_{array}$  values.

**Array Voltage Selection.** Using the performance loss predictor, Voltron selects the minimum value of  $V_{array}$  that satisfies the given user target for performance loss. Algorithm 1 depicts the array voltage selection component of Voltron. The voltage selection algorithm is executed at periodic intervals throughout the runtime of an application. During each interval, the application's memory demand is profiled. At the end of an interval, Voltron uses the profile to iteratively compare the performance loss target to the predicted performance loss incurred by each voltage level, starting from a minimum value of 0.90V. Then, Voltron selects the minimum  $V_{array}$  that does not exceed the performance loss target and uses this selected  $V_{array}$  as the DRAM supply voltage in the subsequent interval. In our evaluation, we provide Voltron with a total of 10 voltage levels (every 0.05V step from 0.90V to 1.35V) for selection.

#### 5.3 Implementation

Voltron's two components require modest modifications to different parts of the system. In order to support array voltage scaling, Voltron requires minor changes to the power delivery network of DIMMs, as commerciallyavailable DIMMs currently use a single supply voltage for both the DRAM array and the peripheral circuitry. Note

Understanding Reduced-Voltage Operation in Modern DRAM Devices • 9:21

| Alg | corithm 1 Array Voltage Selection               |                                                                                                 |

|-----|-------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 1   | SelectArrayVoltage( <i>target_loss</i> )        |                                                                                                 |

| 2   | for each interval                               | ▶ Enter at the end of an interval                                                               |

| 3   | <pre>profile = GetMemoryProfile()</pre>         |                                                                                                 |

| 4   | $NextV_{array} = 1.35$                          |                                                                                                 |

| 5   | for $V_{array} \leftarrow 0.9$ to 1.3           | $\triangleright$ Search for the smallest $V_{array}$ that satisfies the performance loss target |

| 6   | <pre>predicted_loss = Predict(Latency</pre>     | ( <i>V</i> <sub>array</sub> ), profile.MPKI, profile.StallTime) > Predict performance loss      |

| 7   | <b>if</b> predicted_loss ≤ target_loss <b>t</b> | <b>hen</b> > Compare the predicted loss to the target                                           |

| 8   | $NextV_{array} = V_{array}$                     | $\triangleright$ Use the current $V_{array}$ for the next interval                              |

| 9   | break                                           | •                                                                                               |

| 10  | ApplyVoltage(NextVarray)                        | ▷ Apply the new $V_{array}$ for the next interval                                               |

that this supply voltage goes through *separate* power pins:  $V_{DD}$  and  $V_{DDQ}$  for the DRAM array and peripheral circuitry, respectively, on a modern DRAM chip [92]. Therefore, to enable independent voltage adjustment, we propose to partition the power delivery network on the DIMM into two domains: one domain to supply only the DRAM array ( $V_{DD}$ ) and the other domain to supply only the peripheral circuitry ( $V_{DDQ}$ ).

Performance-aware voltage control requires (*i*) performance monitoring hardware that records the MPKI and memory stall time of each application; and (*ii*) a control algorithm block, which predicts the performance loss at different  $V_{array}$  values and accordingly selects the smallest acceptable  $V_{array}$ . Voltron utilizes the performance counters that exist in most modern CPUs to perform performance monitoring, thus requiring no additional hardware overhead. Voltron reads these counter values and feeds them into the array voltage selection algorithm, which is implemented in the system software layer. Although reading the performance monitors has a small amount of software overhead, we believe the overhead is negligible because we do so only at the end of each interval (i.e., every four million cycles in most of our evaluations; see sensitivity studies in Section 6.8).

Voltron periodically executes this performance-aware voltage control mechanism during the runtime of the target application. During each time interval, Voltron monitors the application's behavior through hardware counters. At the end of an interval, the system software executes the array voltage selection algorithm to select the predicted  $V_{array}$  and accordingly adjust the timing parameters stored in the memory controller for activation, restoration, and precharge. Note that there could be other (e.g., completely hardware-based) implementations of Voltron. We leave a detailed explanation of different implementations to future work.

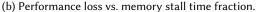

### 6 SYSTEM EVALUATION

In this section, we evaluate the system-level performance and energy impact of Voltron. We present our evaluation methodology in Section 6.1. Next, we study the energy savings and performance loss when we use array voltage scaling without any control (Section 6.2). We study how performance-aware voltage control delivers overall system energy reduction with only a modest amount of performance loss (Sections 6.3 and 6.4). We then evaluate an enhanced version of Voltron, which exploits spatial error locality (Section 6.5). Finally, Sections 6.6 to 6.8 present sensitivity studies of Voltron to various system and algorithm parameters.

# 6.1 Methodology

We evaluate Voltron using Ramulator [63], a detailed and and cycle-accurate open-source DRAM simulator [2], integrated with a multi-core performance simulator. We model a low-power mobile system that consists of 4 ARM cores and DDR3L DRAM. Table 2 shows our system parameters. Such a system resembles existing commodity devices, such as the Google Chromebook [42] or the NVIDIA SHIELD tablet [105]. To model power and energy

#### 9:22 • K. K. Chang et al.

consumption, we use McPAT [79] for the processor and DRAMPower [18] for the DRAM-based memory system. We open-source the code of Voltron [3].

| Processor            | 4 ARM Cortex-A9 cores [11], 2GHz,<br>192-entry instruction window |

|----------------------|-------------------------------------------------------------------|

| Cache                | L1: 64KB/core, L2: 512KB/core, L3: 2MB shared                     |

| Memory<br>Controller | 64/64-entry read/write request queue, FR-FCFS [110, 145]          |

| DRAM                 | DDR3L-1600 [51]<br>2 channels (1 rank and 8 banks per channel)    |

|                      | Table 2. Evaluated system configuration                           |

Table 2. Evaluated system configuration.

Table 3 lists the latency values we evaluate for each DRAM array voltage ( $V_{array}$ ). The latency values are obtained from our SPICE model using data from real devices (Section 4.2), which is available online [3].<sup>8</sup> To account for manufacturing process variation, we conservatively add in the same latency guardband (i.e., 38%) used by manufacturers at the nominal voltage level of 1.35V to each of our latency values. We then round up each latency value to the nearest clock cycle time (i.e., 1.25ns).

| Varray | tRCD - tRP - tRAS (ns) | V <sub>array</sub> | tRCD - tRP - tRAS (ns) |

|--------|------------------------|--------------------|------------------------|

| 1.35   | 13.75 - 13.75 - 36.25  | 1.10               | 15.00 - 16.25 - 40.00  |

| 1.30   | 13.75 - 13.75 - 36.25  | 1.05               | 16.25 - 17.50 - 41.25  |

| 1.25   | 13.75 - 15.00 - 36.25  | 1.00               | 17.50 - 18.75 - 45.00  |