Design Automation Research Group

NVIDIA Design Automation Research Group

Welcome to the homepage of NVIDIA’s Design Automation Research group. We do research in novel design automation methods to improve chip design quality and design productivity. Our projects cover many chip design processes, from RTL design to verification, from digital design to analog design, and from logic synthesis and physical design to sign-off and design-for-manufacturing. Key research areas include:

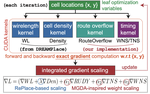

- GPU-accelerated EDA tools: GPU computing power increases at a much faster pace than CPU. There is a great opportunity to scale EDA tools’ performance on GPU.

- AI for EDA: We explore AI methods such as Bayesian optimization, reinforcement learning, and generative AI to solve difficult EDA problems.

- LLM for Chip Design: Large language model is changing the world. We train custom LLMs for chip design and develop systems that leverage LLMs to perform chip design tasks.

We collaborate with other NVIDIA research groups, internal HW design teams, as well as major university research groups and commercial companies. Graduate students interested in interning with us are welcome to reach out directly to team members for more details.