The Even/Odd Synchronizer: A Fast, All-Digital Periodic Synchronizer

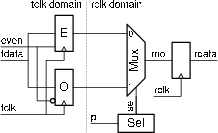

We describe an all-digital synchronizer that moves multi-bit signals between two periodic clock domains with an average delay of slightly more than a half cycle and an arbitrarily small probability of synchronization failure. The synchronizer operates by measuring the relative frequency of the two periodic clocks and using this frequency measurement, along with a phase detection, to compute a phase estimate. Interval arithmetic is used for the phase estimate to account for uncertainty. The transmitter writes a pair of registers on alternating clock cycles and the receiver uses the estimate of the transmitter's phase to always select the most recently written value that is safe to sample. We show how to incorporate this design into a FIFO to give a fast periodic synchronizer with flow control. We present a number-theoretic argument that the synchronizer works for all frequency combinations. An implementation of the ynchronizer using standard cells is also presented.

Publication Date

Research Area

Uploaded Files

Copyright

This material is posted here with permission of the IEEE. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.