Designing Efficient Heterogeneous Memory Architectures

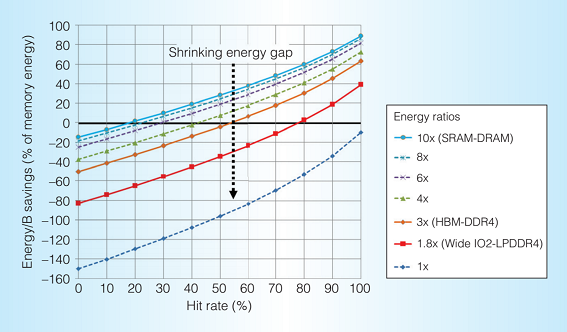

The authors' model of energy, bandwidth, and latency for DRAM technologies enables exploration of memory hierarchies that combine heterogeneous memory technologies with different attributes. Analysis shows that the gap between on- and off-package DRAM technologies is narrower than that found between cache layers in traditional memory hierarchies. Thus, heterogeneous memory caches must achieve high hit rates or risk degrading both system energy and bandwidth efficiency.

Publication Date

Published in

Research Area

External Links

Copyright

This material is posted here with permission of the IEEE. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.