Exploiting Asymmetry in Booth-Encoded Multipliers for Reduced Energy Multiplication

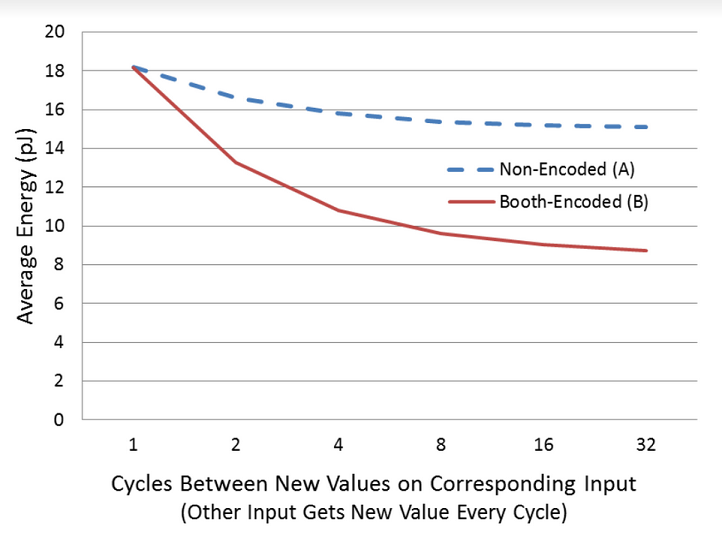

Booth Encoding is a common technique utilized in the design of high-speed multipliers. These multipliers typically encode just one operand of the multiplier, and this asymmetry results in different power characteristics as each input transitions to the next value in a pipelined design. Relative to the non-encoded input, changes on the Booth-encoded input induce more signal transitions requiring ~73% more multiplier array energy. This paper proposes low-overhead approaches to take advantage of this asymmetric behavior to reduce the energy of multiplication operations in pipelined SIMD architectures like GPUs. Compiler-based approaches that apply constant or uniform inputs to the Booth-encoded input of the multiplier can save 4.8% of multiplier energy on average. An additional 1.5% savings can be achieved with dynamic detection and steering of uniform inputs.

Publication Date

Research Area

External Links

Uploaded Files

Copyright

This material is posted here with permission of the IEEE. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.