ParaGraph: Layout Parasitics and Device Parameter Prediction using Graph Neural Networks

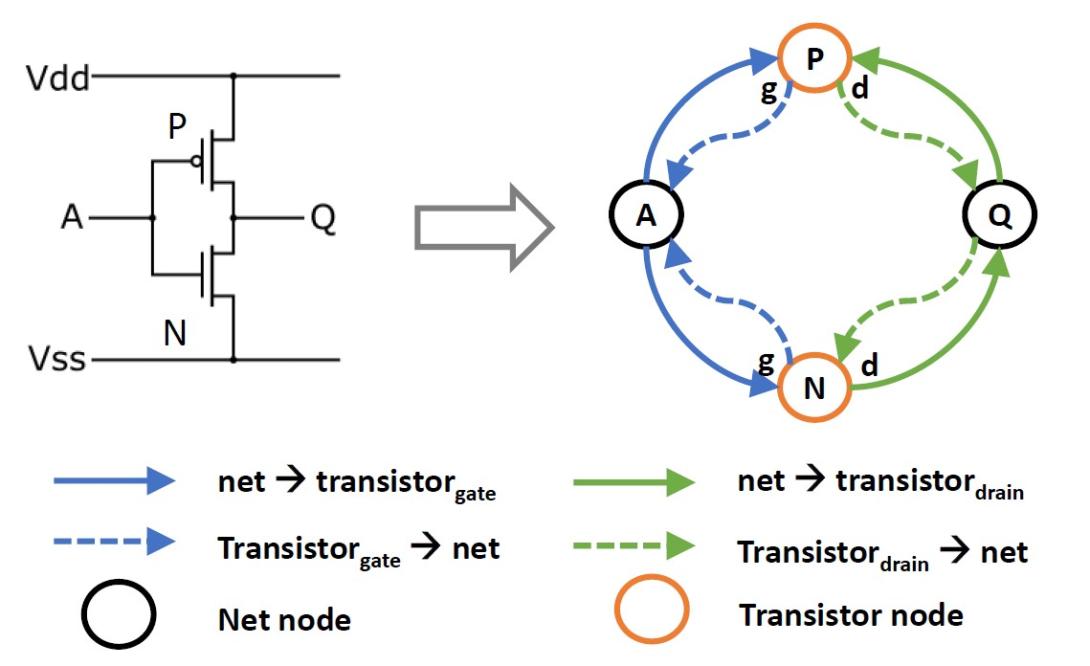

Layout-dependent parasitics and device parameters significantly impact integrated circuit performance and are often the cause of slow convergences between schematic and layout designs. Circuit designers typically estimate parasitics from past experience, resulting in variability between designers and the potential for inaccuracies. In this paper, we present ParaGraph: a graph neural network model to predict net parasitics and device parameters by converting circuit schematics into graphs and leveraging key modeling techniques based on GraphSage, Relation GCN and Graph Attention Networks. Furthermore, the use of ensemble modeling increases model accuracy over a large range of prediction values. Trained on a large dataset of industrial circuits, the model achieves an average prediction R2 of 0.772 (110% better than XGBoost) and reduces average simulation errors from over 100% with designer’s estimation to less than 10%.

Publication Date

Published in

Uploaded Files

Copyright

This material is posted here with permission of the IEEE. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.