DeePattern: Layout Pattern Generation with Transforming Convolutional Auto-Encoder

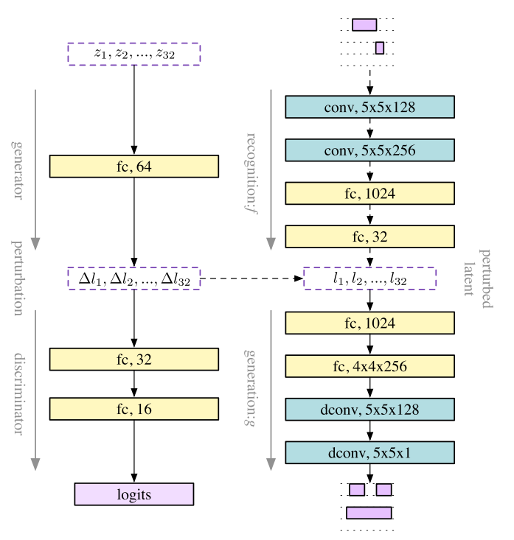

VLSI layout patterns provide critical resources in various design for manufacturability research, from early technology node development to back-end design and sign-off flows. However, a diverse layout pattern library is not always available due to long logic-to-chip design cycle, which slows down the technology node development procedure. To address this issue, in this paper, we explore the capability of generative machine learning models to synthesize layout patterns. A transforming convolutional auto-encoder (TCAE) family is developed to learn vector-based instantiation of squish pattern topologies. We show our TCAE models can capture simple design rules and enlarge the existing squish topology space under certain transformations. With adaptive configurations, the proposed G-TCAE framework allows both massive pattern generation and context-specific pattern generation. Geometry information of each squish topology is obtained from an associated linear system derived from design rule constraints. Experiments on 7nm EUV designs show that our framework can more effectively generate diverse pattern libraries with DRC-clean patterns compared to a state-of-the-art industrial layout pattern generator.

Publication Date

Published in

Research Area

Award

Copyright

This material is posted here with permission of the IEEE. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.