A Pausible Bisynchronous FIFO for GALS Systems

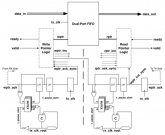

Many of the challenges of modern SoC design can be mitigated or eliminated with globally asynchronous, locally synchronous (GALS) design techniques. Partitioning a design into many synchronous islands introduces myriad asynchronous boundary crossings which typically incur high latency. We have designed a pausible bisynchronous FIFO that achieves low inter- face latency with a pausible clocking scheme. While traditional synchronizers have a non-zero probability of metastability and er- ror, pausible clocking enables error-free operation by permitting infrequent slowdowns in the clock rate. Unlike prior pausible syn- chronizers, our circuit employs standard two-ported synchronous FIFOs, common circuit elements that integrate well with standard toolflows. The pausible bisynchronous FIFO achieves an average latency of 1.34 cycles across an asynchronous interface while using less energy and area than traditional synchronizers.

Publication Date

Published in

Research Area

Uploaded Files

Copyright

This material is posted here with permission of the IEEE. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.